# **CML Semiconductor Products**

**PRODUCT INFORMATION**

# FX214 FX224

VSB\* Audio Scrambler

Publication D/214/3 July 1994

## Features/Applications

- \*Variable Split-Band Frequency Inversion Voice Scrambler

- 32 Programmable Split Frequencies

- CTCSS HP Filter

- High Recovered Audio Quality

- Low-Power 5 Volt CMOS

- Half-Duplex Switching

- Powersave Facility

- Mobile or Cellular Radio Applications

- Fixed or Rolling Code Applications

- Serial/Parallel Load Options: FX214 (Serial), FX224 (Parallel),

- DIL and SMD Package Options

# FX214 FX224

# **Brief Description**

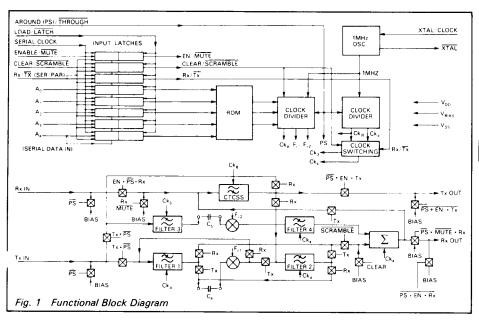

The FX214 and 224 are low-power CMOS LSI devices designed as Variable Split-Band (VSB) voice scramblers.

The device uses separate Rx and Tx paths which are switched for half-duplex operation. To prevent interference from sub-audio products, an on-chip Continuous Tone Controlled Squelch System (CTCSS) highpass filter is automatically switched to the input in Rx and to the output in Tx.

Scrambling is achieved by splitting the input voice frequencies into upper and lower frequency bands using switched capacitor filters, modulating each band with selected carrier frequencies to "frequency invert" the bands and then summing the output.

A total of 32 different split-point and carrier frequency combinations are externally programmable using a 5-bit code; this code can be either fixed or varying (rolling), for greater security.

'Sync/Speech Mute', 'Powersave', 'Clear' and 'Audio-Bypass' facilities are controlled via external commands.

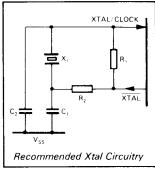

Timing and filter clocks are derived internally from an on-chip oscillator requiring only an external 1MHz Xtal or clock pulse input.

This device demonstrates high baseband and carrier frequency rejection with good 'recovered audio' quality. Serial or parallel command loading functions are available in both DIL and SMD Packages

# **Pin Functions**

| FX<br>214J | FX<br>214LG<br>214L2 | FX<br>224J            | FX<br>224LG<br>224LS  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|----------------------|-----------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

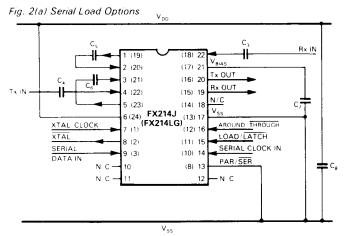

| 7          | 1                    | 1                     | 1                     | Xtal/Clock: Input to the clock oscillator inverter. A 1MHz Xtal input or externally derived 1MHz clock is injected here. See Figure 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 8          | 2                    | 2                     | 2                     | Xtal: Output of the clock oscillator inverter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

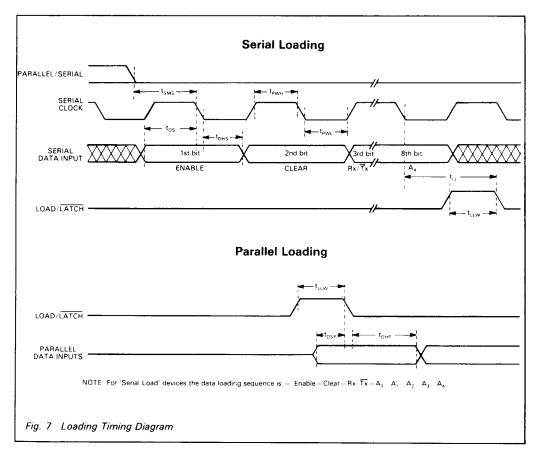

| 9          | 3                    |                       |                       | <b>Serial Data Input:</b> This pin is used, on devices wired in the serial loading mode, to input an 8- bit word representing the digital control functions. This word is loaded using the serial data clock and is input in the following sequence: ENABLE; CLEAR; $Rx/Tx$ ; $A_0$ ; $A_1$ ; $A_2$ ; $A_3$ , $A_4$ , with the Load/Latch being operated on completion. See Timing Diagram Figure 7.                                                                                                                                                                                                                                                                                        |

|            |                      | 3<br>4<br>5<br>6<br>7 | 3<br>4<br>5<br>6<br>7 | A <sub>4</sub> : A <sub>3</sub> : whose code defines the split point frequency and the High and Low band carrier frquencies. Each of the 5 input pins have a $1M\Omega$ internal pullup resistor. Table 2 contains programming information .                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            |                      | 8                     | 8                     | <b>Rx/Tx:</b> This digital input selects the Receive or Transmit paths and configures Upperband and Lowerband filter bandwidths whilst setting the CTCSS High Pass Filter position in the signal path. See Table 1 and Figures 5 and 6. $1M\Omega$ internal pullup resistor [Rx].                                                                                                                                                                                                                                                                                                                                                                                                           |

| 13         | 8                    |                       |                       | <b>Parallel/Serial:</b> This pin defines the loading mode of the digital function inputs. In the parallel load devices this pin has no external connections. For serial load devices this pin must be externally conected to $V_{\rm SS}$ . This pin on all devices has an $1 {\rm M}\Omega$ internal pullup resistor.                                                                                                                                                                                                                                                                                                                                                                      |

|            |                      | 9                     | 9                     | Clear/Scramble: This digital input puts the device 'Clear' or 'Frequency Inversion' mode by controlling the application of carrier frequency to the upper and lower band balanced modulators. In 'Scramble' the balanced modulator carrier frequency values are selected by the split point address $A_0$ - $A_4$ [Table 2]. In 'Clear' carriers are turned off and the balanced modulators are bypassed internally, the lower band is not added to the output signal. $1M\Omega$ internal resistor [Clear].                                                                                                                                                                                |

|            |                      | 10                    | 10                    | <b>Enable/Mute:</b> This digital function is used to disable receive or transmit signal paths for rolling code synchronization whilst maintaining bias conditions. To allow synchronizing information to be transmitted, or receiver audio output to be removed during sync periods, a logic '1' will enable' a logic '0' will disable the selected $[Rx/Tx]$ audio path. See Table 1. $1M\Omega$ internal pullup resistor.                                                                                                                                                                                                                                                                 |

| 14         | 10                   |                       |                       | Serial Clock Input: The externally applied data clock frequency used to shift input data along on devices wired in the Serial loading mode. One full data clock cycle is required to shift one data bit completely into the register. See Timing Diagram Figure 7. This pin has a $1M\Omega$ internal pullup resistor.                                                                                                                                                                                                                                                                                                                                                                      |

| 15         | 11                   | 11                    | 11                    | <b>Load/Latch:</b> Controls the loading of the 8 digital function inputs: ENABLE; CLEAR; Rx/Tx; $A_0$ - $A_4$ into the internal register. When this pin is '1' all 8 inputs are transparent and new data acts directly. For controlled changing of parameters in the parallel mode Load/Latch must be kept at logic '0' whilst a new function is loaded, then Load/Latch strobed 0-1-0 to latch the inputs in. For serial loading the data should be loaded with Load/Latch at logic '0' and then Load/Latch strobed 0-1-0 on completion of data loading. $1M\Omega$ internal pullup resistor. See Figure 7. NOTE: Serial and/or parallel loading functions are dependant upon device type. |

# **Pin Functions**

| Ev         |                      |            |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|----------------------|------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FX<br>214J | FX<br>214LG<br>214L2 | FX<br>224J | FX<br>224LG<br>224LS |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 16         | 12                   | 12         | 12                   | <b>Around [Powersave]/Through:</b> This digital input is used, when logic '1' to put the device into a powersave condition where all parts of the device except the 1MHz oscillator circuits are shut down, and signal input and output lines made opencircuit, free of all bias. This allows signal paths to be routed externally around the device. whilst reducing current consumption. A logic '0' enables the device to work normally as shown in Table 1. $1M\Omega$ internal pullup resistor.  |

| 17         | 13                   | 13         | 13                   | V <sub>ss</sub> : Negative Supply [GND].                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 18         | 14                   | 14         | 14                   | Internally connected , leave open circuit .                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 19         | 15                   | 15         | 15                   | <b>Rx Output:</b> The processed audio signal output. This pin is held at dc 'bias' voltage for all functions except Powersave. This buffered output is driven by the Summer circuit in the Rx mode. Signal paths and bias levels are detailed in the Table 1 and Figure 6.                                                                                                                                                                                                                            |

| 20         | 16                   | 16         | 16                   | <b>Tx Output:</b> The processed audio output for the transmission channel. This pin is held at a dc 'bias' for all functions except Powersave. This summed and buffered signal is passed through the CTCSS High Pass Filter to the output pin in the Tx mode. Signal paths and bias levels are detailed in Table 1 and Figure 5.                                                                                                                                                                      |

| 21         | 17                   | 17         | 17                   | $V_{\text{BIAS}}$ : Normally at $V_{\text{DD}}/2$ this pin requires an external decoupling capacitor to $V_{\text{SS}}$ .                                                                                                                                                                                                                                                                                                                                                                             |

| 22         | 18                   | 18         | 18                   | <b>Rx Input:</b> The analogue received audio signal input. This pin is held at a dc 'bias' voltage by a $300 \text{k}\Omega$ on-chip bias resistor which is selected for all functions except Powersave, and therefore requires to be connected to external circuitry by a capacitor, $C_3$ . See Figure 2. This input is routed through the CTCSS High Pass Filter in Rx mode to remove sub-audio frequencies from the voiceband. Signal paths and bias levels are detailed in Table 1 and Figure 6. |

| 1          | 19                   | 19         | 19                   | <b>Highband Filter Output:</b> The output of the Input Filter of the Upperband arm. The Rx/Tx function sets the lowpass filter at 3400Hz or 2700Hz respectively. This output must be connected to the Highband Balanced Modulator input via capacitor $C_{\rm s}$ . See Figure 2.                                                                                                                                                                                                                     |

| 2          | 20                   | 20         | 20                   | <b>Highband Balanced Modulator Input:</b> The input to the Balanced Modulator of the Upperband arm. This input must be connected to the Highband Filter Output via capacitor $\mathbf{C}_{\mathrm{s}}$ .                                                                                                                                                                                                                                                                                              |

| 3          | 21                   | 21         | 21                   | <b>Lowband Balanced Modulator Input:</b> The input to the Balanced Modulator of the Lowerband arm. This input must be connected to the Lowerband Filter Output with capacitor $C_{\rm g}$ .                                                                                                                                                                                                                                                                                                           |

| 4          | 22                   | 22         | 22                   | Tx Input: This is the analogue 'Clear' audio input for the VSB scrambler. This pin is held at a dc 'bias' voltage by a $300 \text{K}\Omega$ on-chip bias resistor which is selected for all functions except Powersave, and therefore requires to be connected to external circuitry by $\text{C}_4$ . This input, in the Tx mode, is connected to Upper and Lowerband input filters, signal paths and bias levels are detailed in Table 1 and Figure 5.                                              |

| 5          | 23                   | 23         | 23                   | <b>Lowband Filter Output:</b> The output of the Input Filter of the Lowerband arm, the $Rx/Tx$ function determines which filter is used [Filter 1 or 2]. Figures 5 and 6. This output must be connected to the Lowerband Balanced Modulator Input via $C_6$ .                                                                                                                                                                                                                                         |

| 6          | 24                   | 24         | 24                   | V <sub>DD</sub> : A single + 5V supply is required.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

# **Component Connections**

#### Not Connected

FX214J 10, 11, 12, 18\* FX214LG 4, 5, 6, 7, 9, 14\* FX224J 14\*

FX224LG 14\*

\*Internally connected, do not connect to.

Fig. 2(b) Parallel Load Options  $V_{\underline{D}\underline{D}}$ XTAL. CLOCK XTAL 23 22 21 PROGRAMMING INPUTS 20 FX224J 19 FX224LG 18 - Rx IN Rx Tx 17 CLEAR · SCRAMBLE Tx OUT 16 ENABLE/MUTE Rx OUT 15 LOAD LATCH N/C 14 AROUND THROUGH 13  $V_{ss}$ **C**, Vss

Xtal circuitry shown is in accordance with CML Application Note D/XT/1 April '86.

| Component References |                                                                              |  |  |  |

|----------------------|------------------------------------------------------------------------------|--|--|--|

| Component            | Unit Value                                                                   |  |  |  |

| RROOGE 456.          | 1M<br>Selectable<br>33p<br>68p<br>15n<br>15n<br>1.0µ<br>1.0µ<br>1.0µ<br>1.0µ |  |  |  |

Tolerance Resistors  $\pm~10\%$  Capacitors  $\pm~20\%$  C<sub>5</sub> and C<sub>6</sub> are coupling capacitors between filter outputs and balanced modulator inputs.

Fig. 2 External Component Connections

## **Application Information**

This device can be used in 'Scramble' (frequency inversion) or 'Clear' speech modes. The inversion frequencies, when selected are controlled by the ROM address code (table 2). Keeping the code in one state (fixed) is the simplest form of operation. A more secure method is to continually change the ROM address code (rolling code) therefore changing split-point and carrier frequencies. This method requires some external form of code change generation with synchronization between transmit and receive stations. Many variations of code sequence are possible.

The recommended external component connections are shown in figure 2. In the Scramble mode, Splitpoint and Low and High band carrier frequencies ( $F_c1$ ,  $F_c2$ ) are selected and set in accordance with the ROM address code present at the inputs  $A_0$  to  $A_4$ , See Table 2.

During the Clear speech function both Lower and Upperband filter arms are selected (figures 5 or 6), the carrier frequencies are turned off and the balanced modulators are bypassed internally. The Low band audio is removed from the output signal prior to summation.

#### Enable/Mute

To enable code synchronization to be transmitted the speech output can be interrupted with the Enable/Mute function. A logic '0' will isolate the whole device whilst leaving the audio input and output pins at bias level. See Table 1.

#### **Powersave**

When the Around/Through function is at a logic '1' the device is in the powersave condition. Audio signals may be hardwired around the device normally as the input and output pins are open circuit. See Table 1.

| Effect of Chosen Function on Inputs and Outputs |       | CHOSEN FUNCTION |              |              |                   |  |  |

|-------------------------------------------------|-------|-----------------|--------------|--------------|-------------------|--|--|

|                                                 |       | Rx = '1'        | Tx = '0'     | Mute = '0'   | Around (Powersave |  |  |

| Rx Input                                        | Path  | Enabled         | Disconnect   | Disconnect   | High Impedance    |  |  |

|                                                 | Level | Bias            | Bias         | Bias         | 1 mgn impedance   |  |  |

| Rx Output                                       | Path  | Enabled         | Disconnected | Disconnect   | High Impedance    |  |  |

| Output                                          | Level | Bias            | Bias         | Bias         | righ impedance    |  |  |

| Tx Input                                        | Path  | Disconnected    | Enabled      | Enabled      | High Impadance    |  |  |

|                                                 | Level | Bias            | Bias         | Bias         | High Impedance    |  |  |

| Tx Output                                       | Path  | Disconnected    | Enabled      | Disconnected | High Impadance    |  |  |

| in output                                       | Level | Bias            | Bias         | Bias         | High Impedance    |  |  |

Table 1 Functions Influencing Signal Paths

| ROM Address<br>A <sub>4</sub> -A <sub>0</sub>                                                                     | Split Point<br>Hz                                                                                                            | Low Band<br>Carrier, Hz<br>f <sub>c1</sub>                                                                                   | High Band<br>Carrier, Hz<br>f <sub>c2</sub>                                                                                          |

|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 00000<br>00001<br>00001<br>00010<br>00101<br>00101<br>00110<br>00111<br>01000<br>01001<br>01011<br>01110<br>01110 | 2800<br>2625<br>2470<br>2333<br>2210<br>2100<br>2000<br>1909<br>1826<br>1750<br>1680<br>1555<br>1448<br>1354<br>1272<br>1200 | 3105<br>2923<br>2777<br>2631<br>2512<br>2403<br>2304<br>2212<br>2127<br>2049<br>1984<br>1858<br>1748<br>1655<br>1572<br>1501 | 6172<br>6024<br>5813<br>5681<br>5555<br>5494<br>5376<br>5263<br>5208<br>5102<br>5050<br>4950<br>4950<br>4807<br>4716<br>4629<br>4587 |

| ROM Address<br>A <sub>4</sub> -A <sub>0</sub>                                                                                                         | Split Point<br>Hz                                                                                               | Low Band<br>Carrier, Hz<br>f <sub>c1</sub>                                                                          | High Band<br>Carrier, Hz<br>f <sub>c2</sub>                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 10000<br>10001<br>10010<br>10011<br>10010<br>10101<br>10110<br>10111<br>11000<br>11001<br>11010<br>11011<br>11010<br>11101<br>11101<br>11101<br>11101 | 1135<br>1050<br>1050<br>913<br>857<br>792<br>736<br>688<br>636<br>591<br>552<br>512<br>471<br>428<br>388<br>350 | 1436<br>1351<br>1278<br>1213<br>1157<br>1094<br>1037<br>988<br>936<br>891<br>853<br>813<br>772<br>728<br>688<br>650 | 4504<br>4424<br>4347<br>4310<br>4273<br>4166<br>4132<br>4065<br>4032<br>3968<br>3937<br>3906<br>3846<br>3816<br>3787<br>3731 |

Table 2 ROM Address Programming Table

### **Application Information**

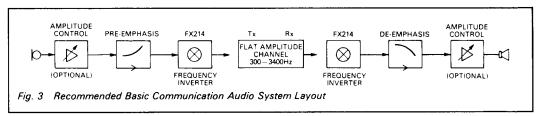

For the following descriptions, the term 'FX214' can be taken to mean FX214 or FX224.

#### **Audio Quality**

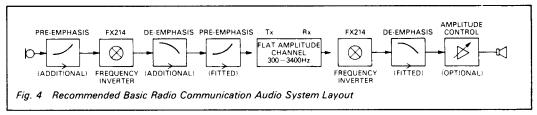

Figure 3 shows the recommended basic audio system layout using added pre- and de-emphasis circuitry to maintain good recovered speech quality. In the Transmit mode *Do Not* pre-emphasise the audio output of the FX214. In the Receive mode de-emphasis should be used after the FX214.

Figure 4 shows the recommended basic audio system layout if it is necessary to install the FX214 within a radio having pre- and de-emphasis circuitry as a standard. This is where post-emphasis access is not possible in the transmitter.

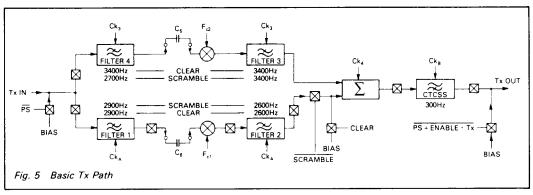

During the Transmit function the Low Pass and CTCSS filters are configured automatically as shown in Figure 5, with cut-off frequencies (-3dB) indicated.

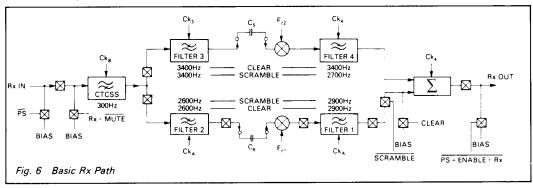

During the Receive function the Low Pass and CTCSS filters are configured automatically as shown in Figure 6, with cut-off frequencies (-3dB) indicated.

## **Electrical Specifications**

### **Absolute Maximum Ratings**

Exceeding the maximum rating can result in device damage. Operation of the device outside the operating limits is not implied.

Supply voltage -0.3V to 7.0V

Total device dissipation @ 25°C 800mW Max.

Derating 10mW/°C

Operating temperature range: FX214J/224J  $-30^{\circ}$ C to  $+85^{\circ}$ C (Ceramic) FX214LG/224LG  $-30^{\circ}$ C to  $+70^{\circ}$ C (Plastic)

| Storage temperature range: | FX214J/224J | -55°C to +70°C (Plastic) | FX214LG/224J | -55°C to +70°C (Plastic) | FX214LG/224LG | -40°C to +85°C (Plastic) |

### **Operating Limits**

All characteristics measured using the following parameters unless otherwise specified:  $V_{DD}=5.0V,\, T_{amb}=25^{\circ}C,\, F_{clk}=1.0MHz,\, Audio\, Level\,Ref:\,0dB=775mVrms.$

| Characteristics                    | See Note  | Min. | Тур.           | Max. | Unit |

|------------------------------------|-----------|------|----------------|------|------|

|                                    |           |      |                |      |      |

| Static Values                      |           |      |                |      |      |

| Supply voltage                     |           | 4.5  | 5              | 5.5  | ٧.   |

| Supply current (Enabled)           |           | _    | .8             | -    | mĄ   |

| Supply current (Powersave)         |           | _    | 1.2            |      | mA   |

| Analogue Input Impedances          |           |      |                |      |      |

| Tx/Rx Input (Enabled)              |           | _    | 100            | _    | kΩ   |

| Tx/Rx Input (Powersave)            |           | 1    |                | _    | MΩ   |

| Balanced Modulator                 |           | _    | 40             | _    | kΩ   |

| Analogue Output Impedances         |           |      |                |      |      |

| Rx Output (Tx Mode)                |           | -    | 100            | _    | kΩ   |

| Rx Output (Rx Mode)                |           | -    | <del>-</del> , | 2    | kΩ   |

| Rx Output (Powersave)              |           | 1    |                | _    | MΩ   |

| Tx Output (Tx Mode)                |           | _    |                | 2    | kΩ   |

| Tx Output (Rx Mode)                |           |      | 100            | _    | kΩ   |

| Tx Output (Powersave)              |           | 1    | _              | _    | ΜΩ   |

| Input LPF                          |           | _    | _              | 1    | kΩ   |

| Digital Values                     |           |      |                |      |      |

| Digital Input Impedance            |           | 100  | _              | _    | kΩ   |

| Dynamic Values                     |           |      |                |      |      |

| Input Logic '1'                    |           | 3.5  |                | _    | V    |

| Input Logic '0'                    |           |      | _              | 1.5  | V    |

| Xtal/Clock Frequency               |           | _    | 1              | _    | MHz  |

| Analogue Input Level               |           | - 18 | _              | + 6  | dB   |

| Carrier Breakthrough               | 1         | _    | - 55           | _    | dB   |

| Baseband Breakthrough              | 1, 2 or 3 | -    | <b>– 33</b>    | _    | dB   |

| Filter Clock Breakthrough          | 1, 2 or 3 | _    | <b>- 50</b>    | _    | dB   |

| Output Noise                       | 1, 4      | _    | <b>- 45</b>    | _    | dB   |

| Passband Characteristics           |           |      |                |      |      |

| Clear Mode                         | 7         |      |                |      |      |

| Passband Gain                      |           | -    | 0              |      | dB   |

| Output Lower 3dB Point (Rx or Tx)  |           | _    | 300            |      | Hz   |

| Output Upper 3dB Point (Rx or Tx)  |           | -    | 3400           | _    | Hz   |

| cramble-Descramble                 | 5         |      |                |      |      |

| Received Signal Passband Gain      | 6         | _    | 0              | _    | dB   |

| Received Signal Lower 3dB Point    |           | _    | 400            | _    | Hz   |

| Received Signal Upper 3dB Point    |           | _    | 2700           | _    | Hz   |

| Transmitted Signal Lower 3dB Point |           | -    | 300            | _    | Hz   |

| Transmitted Signal Upper 3dB Point |           | _    | 3400           | _    | Hz   |

| CTCSS (Highpass Filter)            |           |      |                |      |      |

| - 3dB Point                        |           | _    | 300            | _    | Hz   |

| Passband Gain                      |           | _    | 0              | _    | dB   |

| Stopband Attenuation at f>250 Hz   |           | _    | 40             | _    | dB   |

|                                    |           |      |                |      |      |

|                                    |           |      |                |      |      |

# **Electrical Specifications...**

| Characteristics                                                                                                                                                             | See Note | Min. | Тур. | Max. | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|------|------|------|

| Timing (Figure 7)                                                                                                                                                           |          |      |      |      |      |

| Serial Mode Enable Set Up (t <sub>SMS</sub> )<br>Serial Clock 'High' Pulse Width (t <sub>PWH</sub> )<br>Serial Clock 'Low' Pulse Width (t <sub>PWI</sub> )                  |          | 250  |      | _    | ns   |

| Serial Clock 'High' Pulse Width (tpw/ll)                                                                                                                                    |          | 250  | -    | _    | ns   |

| Serial Clock 'Low' Pulse Width (tp.MI)                                                                                                                                      |          | 250  | _    | -    | ns   |

| Data Set Up Time (t <sub>DS</sub> ) Data Hold Time (t <sub>DHS</sub> ) Load/ <u>Latch</u> Set Up Time (t <sub>LL</sub> ) Load/ <u>Latch</u> Pulse Width (t <sub>LLW</sub> ) |          | 150  |      |      | ns   |

| Data Hold Time (tphs)                                                                                                                                                       |          | 50   | _    | _    | ns   |

| Load/Latch Set Up Time (t, )                                                                                                                                                |          | 250  | _    | _    | ns   |

| Load/Latch Pulse Width (till)                                                                                                                                               |          | 150  | _    |      | ns   |

| Data Set Up Time (t <sub>DSP</sub> ) Data Hold Time (t <sub>DHP</sub> )                                                                                                     |          | 150  | _    | _    | ns   |

| Data Hold Time (tohe)                                                                                                                                                       |          | 20   | -    | _    | ns   |

Notes: 1. Measured at the output of a single device.

2. Tx Mode. 3. Rx Mode.

With input A.C. short-circuited to V<sub>SS</sub>.

Measured at the output of a receiving device in a scrambler-descrambler system with a transmission channel having a flat amplitude response and a bandwidth of 300Hz to 3400Hz and measured relative to the input signal at the transmitting device.

6. Excluding split point ± 150Hz.

7. Measured at the Rx or Tx output pin of a single device.

# **Package Outlines**

The FX214 and FX224 are available in the package styles outlined below. Mechanical package diagrams and specifications are detailed in Section 10 of this document.

Pin 1 identification marking is shown on the relevant diagram and pins on all package styles number anti-clockwise when viewed from the top.

FX214J 22-pin cerdip DIL

(J3)

**Handling Precautions**

The FX214 and FX224 are CMOS LSI circuits which include input protection. However precautions should be taken to prevent static discharges which may cause damage.

FX224J

24-pin cerdip DIL

(J4)

**NOT TO SCALE**

Max. Body Length 27.38mm Max. Body Width 9.75mm NOT TO SCALE

Max. Body Length Max. Body Width 32.03mm 14.81mm

**FX214LG/224LG** 24-pin quad plastic encapsulated bent and cropped (L1)

**NOT TO SCALE**

Max. Body Length Max. Body Width 10.25mm 10.25mm

# Package Outlines .....

FX214L2/224LS

24-lead plastic leaded

chip carrier

NOT TO SCALE

Max. Body Length Max. Body Width 10.40mm

# **Ordering Information**

FX214J 22-pin cerdip DIL (J3)

FX214LG 24-pin quad plastic encapsulated bent and

croppped (L1) **FX214L2** 24-lead plastic leaded chip

carrier

FX224J 24-pin cerdip DIL (J4)

**FX224LG** 24-pin quad plastic

encapsulated bent and

croppped (L1)

**FX224LS** 24-lead plastic leaded chip

carrier (L2)

### **CML Product Data**

In the process of creating a more global image, the three standard product semiconductor companies of CML Microsystems Plc (Consumer Microcircuits Limited (UK), MX-COM, Inc (USA) and CML Microcircuits (Singapore) Pte Ltd) have undergone name changes and, whilst maintaining their separate new names (CML Microcircuits (UK) Ltd, CML Microcircuits (USA) Inc and CML Microcircuits (Singapore) Pte Ltd), now operate under the single title CML Microcircuits.

These companies are all 100% owned operating companies of the CML Microsystems Plc Group and these changes are purely changes of name and do not change any underlying legal entities and hence will have no effect on any agreements or contacts currently in force.

# **CML Microcircuits Product Prefix Codes**

Until the latter part of 1996, the differentiator between products manufactured and sold from MXCOM, Inc. and Consumer Microcircuits Limited were denoted by the prefixes MX and FX respectively. These products use the same silicon etc. and today still carry the same prefixes. In the latter part of 1996, both companies adopted the common prefix: CMX.

This notification is relevant product information to which it is attached.

Company contact information is as below:

COMMUNICATION SEMICONDUCTORS

Oval Park, Langford, Maldon, Essex, CM9 6WG, England Tel: +44 (0)1621 875500 Fax: +44 (0)1621 875600 uk.sales@cmlmicro.com www.cmlmicro.com

COMMUNICATION SEMICONDUCTORS

4800 Bethania Station Road, Winston-Salem, NC 27105, USA Tel: +1 336 744 5050, 0800 638 5577

Fax: +1 336 744 5054 us.sales@cmlmicro.com www.cmlmicro.com

No 2 Kallang Pudding Road, 09-05/ 06 Mactech Industrial Building, Singapore 349307

Tel: +65 7450426 Fax: +65 7452917 sg.sales@cmlmicro.com www.cmlmicro.com

### **CML Product Data**

In the process of creating a more global image, the three standard product semiconductor companies of CML Microsystems Plc (Consumer Microcircuits Limited (UK), MX-COM, Inc (USA) and CML Microcircuits (Singapore) Pte Ltd) have undergone name changes and, whilst maintaining their separate new names (CML Microcircuits (UK) Ltd, CML Microcircuits (USA) Inc and CML Microcircuits (Singapore) Pte Ltd), now operate under the single title CML Microcircuits.

These companies are all 100% owned operating companies of the CML Microsystems Plc Group and these changes are purely changes of name and do not change any underlying legal entities and hence will have no effect on any agreements or contacts currently in force.

# **CML Microcircuits Product Prefix Codes**

Until the latter part of 1996, the differentiator between products manufactured and sold from MXCOM, Inc. and Consumer Microcircuits Limited were denoted by the prefixes MX and FX respectively. These products use the same silicon etc. and today still carry the same prefixes. In the latter part of 1996, both companies adopted the common prefix: CMX.

This notification is relevant product information to which it is attached.

Company contact information is as below:

COMMUNICATION SEMICONDUCTORS

Oval Park, Langford, Maldon, Essex, CM9 6WG, England Tel: +44 (0)1621 875500 Fax: +44 (0)1621 875600 uk.sales@cmlmicro.com www.cmlmicro.com

COMMUNICATION SEMICONDUCTORS

4800 Bethania Station Road, Winston-Salem, NC 27105, USA Tel: +1 336 744 5050, 0800 638 5577

Fax: +1 336 744 5054 us.sales@cmlmicro.com www.cmlmicro.com

No 2 Kallang Pudding Road, 09-05/ 06 Mactech Industrial Building, Singapore 349307

Tel: +65 7450426 Fax: +65 7452917 sg.sales@cmlmicro.com www.cmlmicro.com